p.42

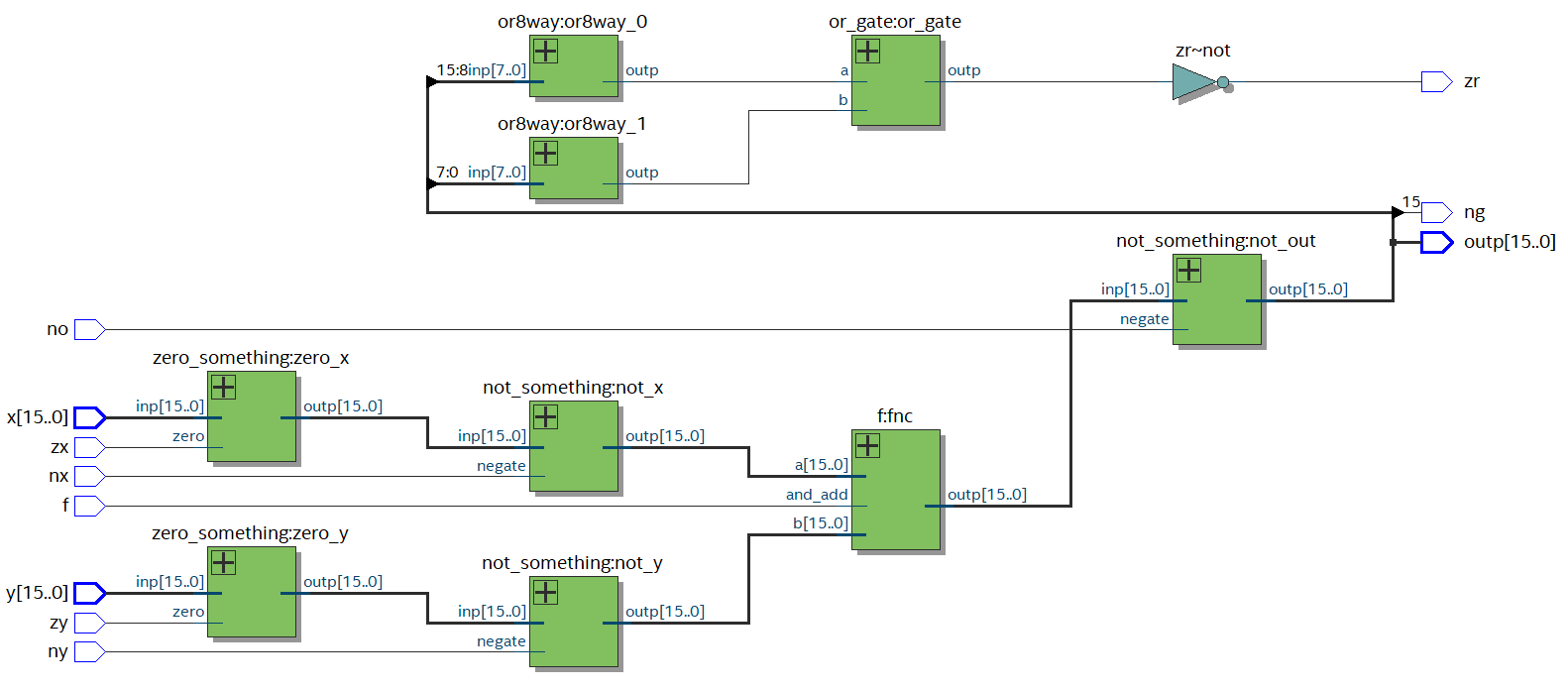

今度はALUを組み立てる。これでChapter 2 Boolean Arithmeticが終わり。

alu:

library ieee; use ieee.std_logic_1164.all; entity alu is port ( x, y: in std_logic_vector(15 downto 0); zx, nx, zy, ny, f, no: in std_logic; outp: out std_logic_vector(15 downto 0); zr, ng: out std_logic ); end entity; architecture behavior of alu is signal temp_zx, temp_nx: std_logic_vector(15 downto 0); signal temp_zy, temp_ny: std_logic_vector(15 downto 0); signal temp_f: std_logic_vector(15 downto 0); signal temp_out: std_logic_vector(15 downto 0); signal temp_or8way_0, temp_or8way_1, temp_or16way: std_logic; begin zero_x: entity work.zero_something port map ( inp => x, zero => zx, -- '0'のときスルー、'1'のとき全部ゼロを出力。 outp => temp_zx ); not_x: entity work.not_something port map ( inp => temp_zx, negate => nx, -- '0'のときスルー、'1'のとき反転。 outp => temp_nx ); zero_y: entity work.zero_something port map ( inp => y, zero => zy, -- '0'のときスルー、'1'のとき全部ゼロを出力。 outp => temp_zy ); not_y: entity work.not_something port map ( inp => temp_zy, negate => ny, -- '0'のときスルー、'1'のとき反転。 outp => temp_ny ); fnc: entity work.f port map ( a => temp_nx, b => temp_ny, and_add => f, -- '0'のときAND、'1'のとき加算。 outp => temp_f ); not_out: entity work.not_something port map ( inp => temp_f, negate => no, -- '0'のときスルー、'1'のとき反転。 outp => temp_out ); outp <= temp_out; or8way_0: entity work.or8way port map ( inp => temp_out(15 downto 8), outp => temp_or8way_0 ); or8way_1: entity work.or8way port map ( inp => temp_out(7 downto 0), outp => temp_or8way_1 ); or_gate: entity work.or_gate port map ( a => temp_or8way_0, b => temp_or8way_1, outp => temp_or16way ); zr <= temp_or16way nand '1'; --出力がゼロのとき'1' ng <= temp_out(15); -- 出力が負のとき'1' end architecture;

Figure 2.5b (p.39)の順番どおりにコントロールビットを与えて試す。入力はx = "0111111111111111"、y = "1111111111111111"のひと組しか試していないが一往正しく動いている。