ALU / 16ビット加算器add16

p.42

今度は16ビット加算器を作る。これまで何度も作っているが再度一から作る。半加算器から作り上げる。nand2tetrisの縛りがあるためかなり面倒くさい。キャリー先読みではなく普通のリプルアダーにする。

half_adder:

library ieee; use ieee.std_logic_1164.all; entity half_adder is port ( a, b: in std_logic; sum, carry: out std_logic ); end entity; architecture behavior of half_adder is begin --sum <= a xor b; sum_p: entity work.xor_gate port map ( a => a, b => b, outp => sum ); --carry <= a and b; carry_p: entity work.and_gate port map ( a => a, b => b, outp => carry ); end architecture;

full_adder:

library ieee; use ieee.std_logic_1164.all; entity full_adder is port ( a, b, c: in std_logic; sum, carry: out std_logic ); end entity; architecture behavior of full_adder is signal sum_1st, carry_1st, carry_2nd: std_logic; begin half_adder_0: entity work.half_adder port map ( a => a, b => b, sum => sum_1st, carry => carry_1st ); half_adder_1: entity work.half_adder port map ( a => sum_1st, b => c, sum => sum, carry => carry_2nd ); or_gate: entity work.or_gate port map ( a => carry_1st, b => carry_2nd, outp => carry ); end architecture;

add16:

library ieee; use ieee.std_logic_1164.all; entity add16 is port ( a, b: in std_logic_vector(15 downto 0); outp: out std_logic_vector(15 downto 0) ); end entity; architecture behavior of add16 is signal temp_carry: std_logic_vector(0 to 15); begin digit_0: entity work.half_adder port map ( a => a(0), b => b(0), sum => outp(0), carry => temp_carry(0) ); digit_others: for i in 1 to 15 generate full_adder: entity work.full_adder port map ( a => a(i) , b => b(i), c => temp_carry(i-1), sum => outp(i), carry => temp_carry(i) ); end generate; end architecture;

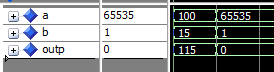

シミュレーション結果: