p.27

今度は下の回路を作る。15個の基本ゲートが全部出来た。これでChapter 1 Boolean Logicは終わり。

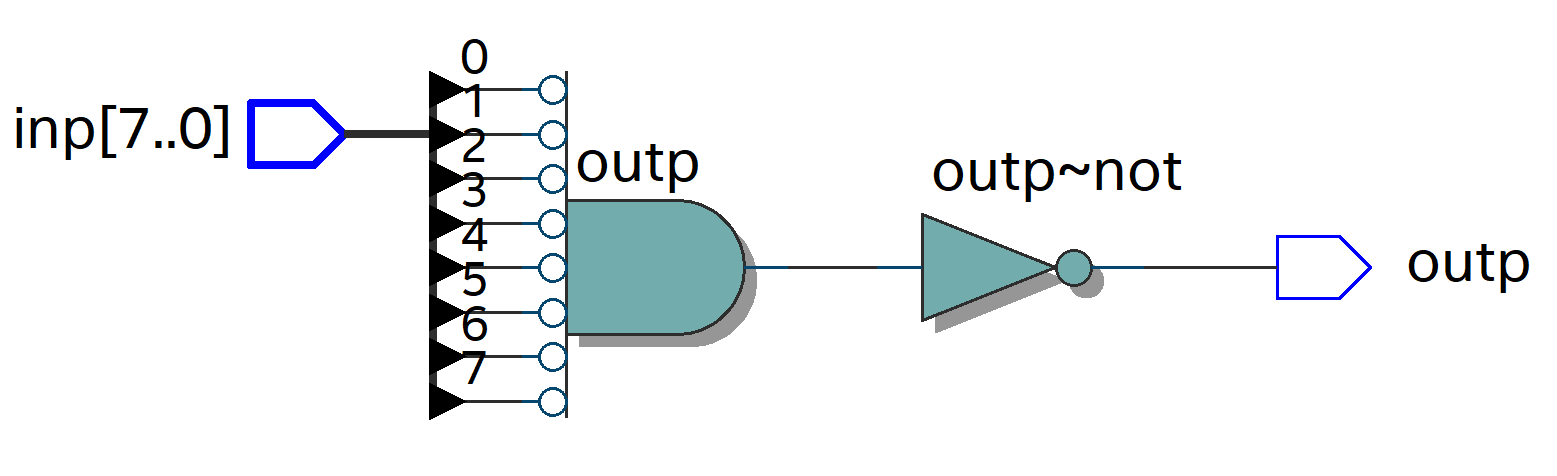

- 8ビット入力のreduction Orゲート

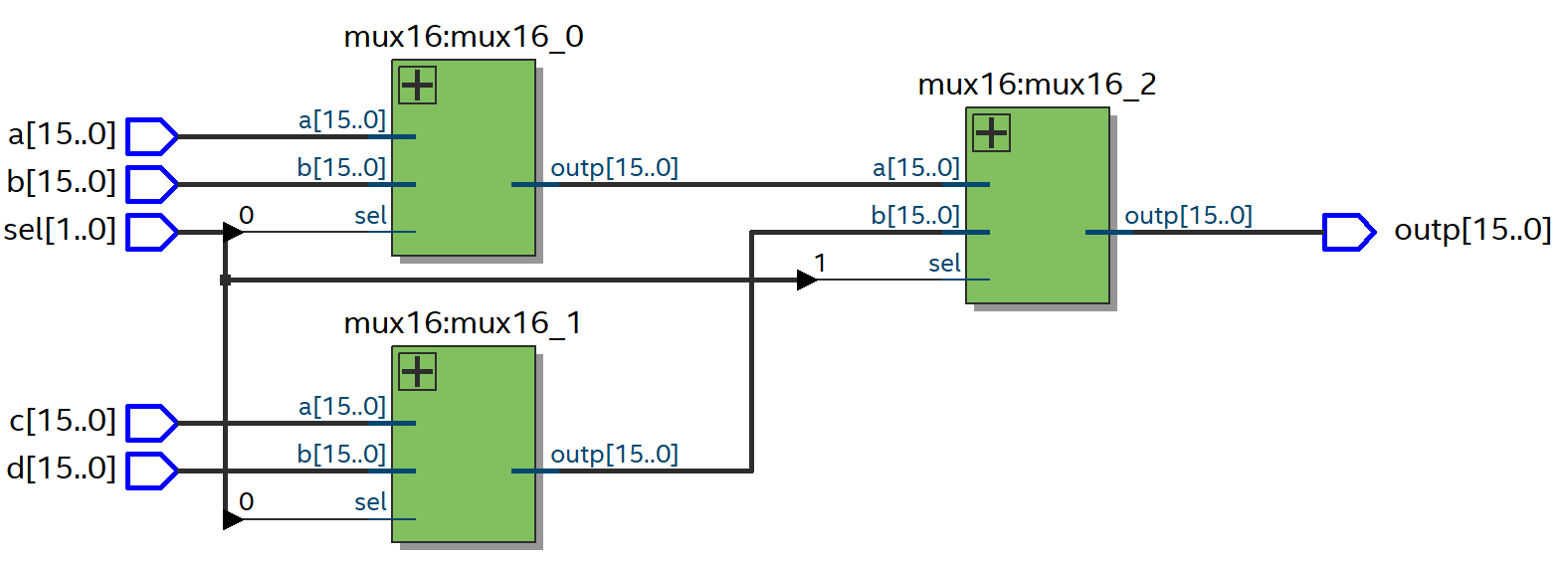

- 16ビット幅×4本のなかから1本を選んで出力する回路

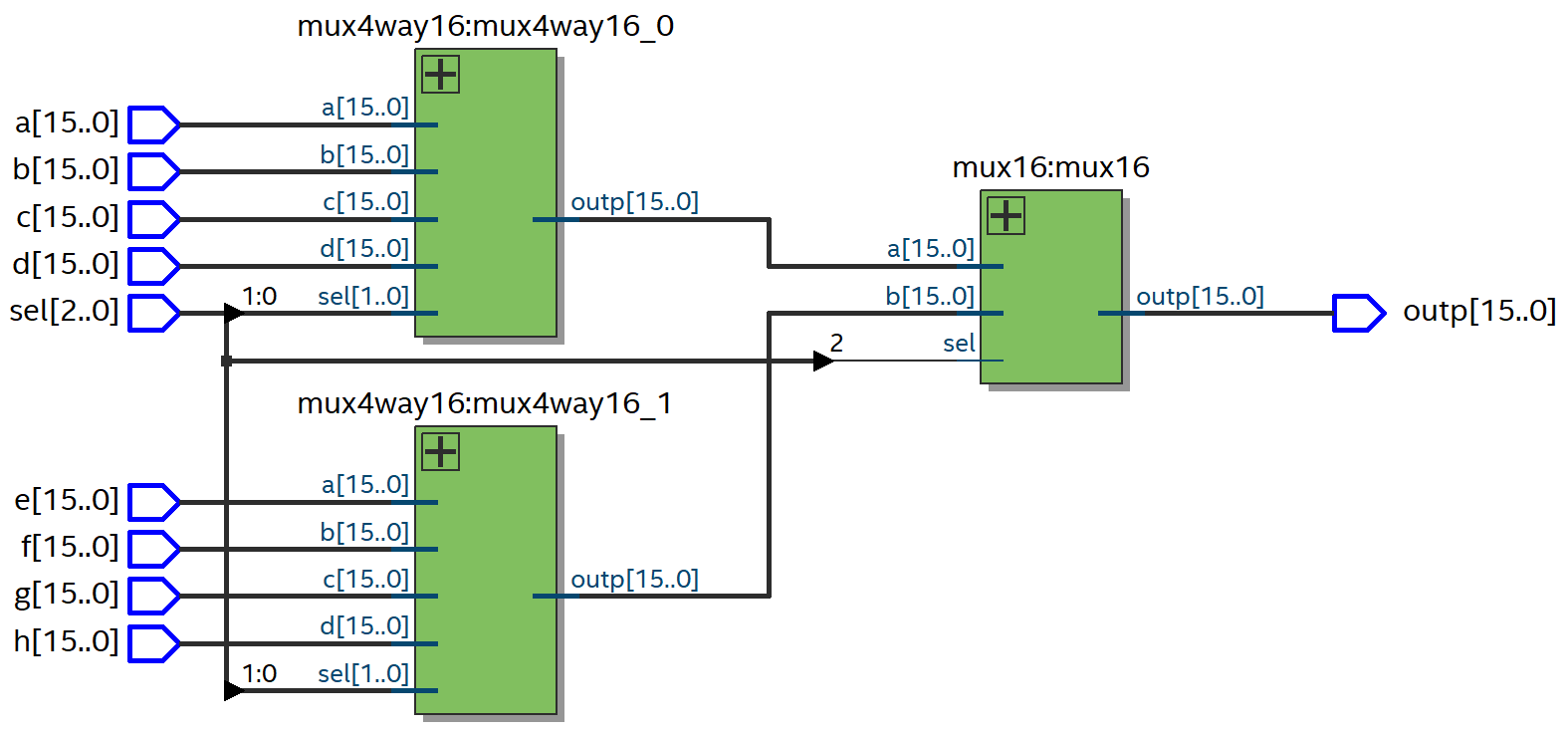

- 16ビット幅×8本のなかから1本を選んで出力する回路

- 4ビットのなかから1ビットを選んで出力する回路

- 8ビットのなかから1ビットを選んで出力する回路

or8way:

library ieee; use ieee.std_logic_1164.all; --いわゆるreduction演算である。 entity or8way is port ( inp: in std_logic_vector(7 downto 0); outp: out std_logic ); end entity; architecture behavior of or8way is signal temp_or: std_logic_vector(0 to 5); begin stage_0: for i in 0 to 3 generate temp_or(i) <= (inp(i*2) nand '1') nand (inp(i*2+1) nand '1'); end generate; stage_1: for i in 0 to 1 generate temp_or(i+4) <= (temp_or(i*2) nand '1') nand (temp_or(i*2+1) nand '1'); end generate; /* temp_or(0) <= (inp(0) nand '1') nand (inp(1) nand '1'); temp_or(1) <= (inp(2) nand '1') nand (inp(3) nand '1'); temp_or(2) <= (inp(4) nand '1') nand (inp(5) nand '1'); temp_or(3) <= (inp(6) nand '1') nand (inp(7) nand '1'); */ /* temp_or(4) <= (temp_or(0) nand '1') nand (temp_or(1) nand '1'); temp_or(5) <= (temp_or(2) nand '1') nand (temp_or(3) nand '1'); */ outp <= (temp_or(4) nand '1') nand (temp_or(5) nand '1'); end architecture;

mux4way16:

library ieee; use ieee.std_logic_1164.all; entity mux4way16 is port ( a, b, c, d: in std_logic_vector(15 downto 0); sel: in std_logic_vector(1 downto 0); outp: out std_logic_vector(15 downto 0) ); end entity; architecture behavior of mux4way16 is signal temp_out_0, temp_out_1: std_logic_vector(15 downto 0); begin mux16_0: entity work.mux16 port map ( a => a, b => b, sel => sel(0), outp => temp_out_0 ); mux16_1: entity work.mux16 port map ( a => c, b => d, sel => sel(0), outp => temp_out_1 ); mux16_2: entity work.mux16 port map ( a => temp_out_0, b => temp_out_1, sel => sel(1), outp => outp ); end architecture;

mux8way16:

library ieee; use ieee.std_logic_1164.all; entity mux8way16 is port ( a, b, c, d, e, f, g, h: in std_logic_vector(15 downto 0); sel: in std_logic_vector(2 downto 0); outp: out std_logic_vector(15 downto 0) ); end entity; architecture behavior of mux8way16 is signal temp_out_0, temp_out_1: std_logic_vector(15 downto 0); begin mux4way16_0: entity work.mux4way16 port map ( a => a, b => b, c => c, d => d, sel => sel(1 downto 0), outp => temp_out_0 ); mux4way16_1: entity work.mux4way16 port map ( a => e, b => f, c => g, d => h, sel => sel(1 downto 0), outp => temp_out_1 ); mux16: entity work.mux16 port map ( a => temp_out_0, b => temp_out_1, sel => sel(2), outp => outp ); end architecture;

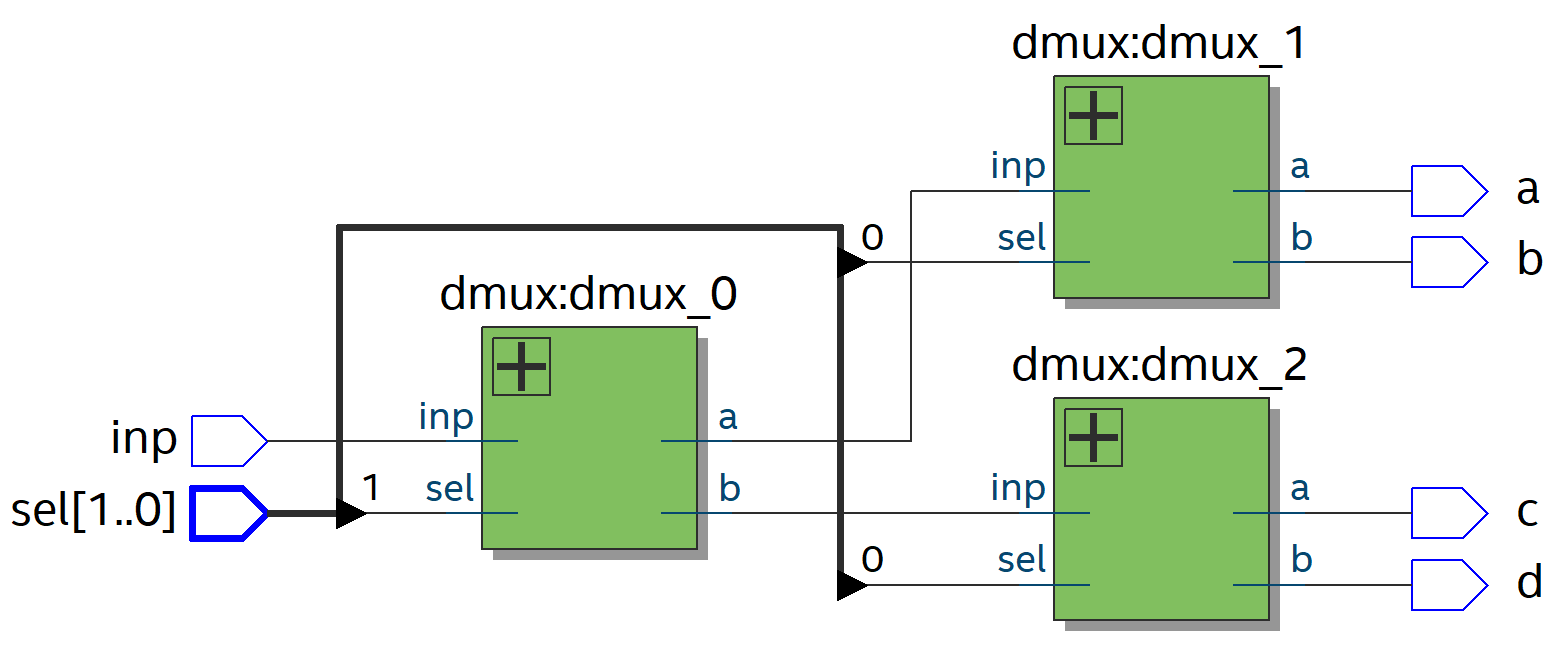

dmux4way:

library ieee; use ieee.std_logic_1164.all; entity dmux4way is port ( inp: in std_logic; sel: in std_logic_vector(1 downto 0); a, b, c, d: out std_logic ); end entity; architecture behavior of dmux4way is signal temp_dmux_0, temp_dmux_1: std_logic; begin dmux_0: entity work.dmux port map ( inp => inp, sel => sel(1), a => temp_dmux_0, b => temp_dmux_1 ); dmux_1: entity work.dmux port map ( inp => temp_dmux_0, sel => sel(0), a => a, b => b ); dmux_2: entity work.dmux port map ( inp => temp_dmux_1, sel => sel(0), a => c, b => d ); end architecture;

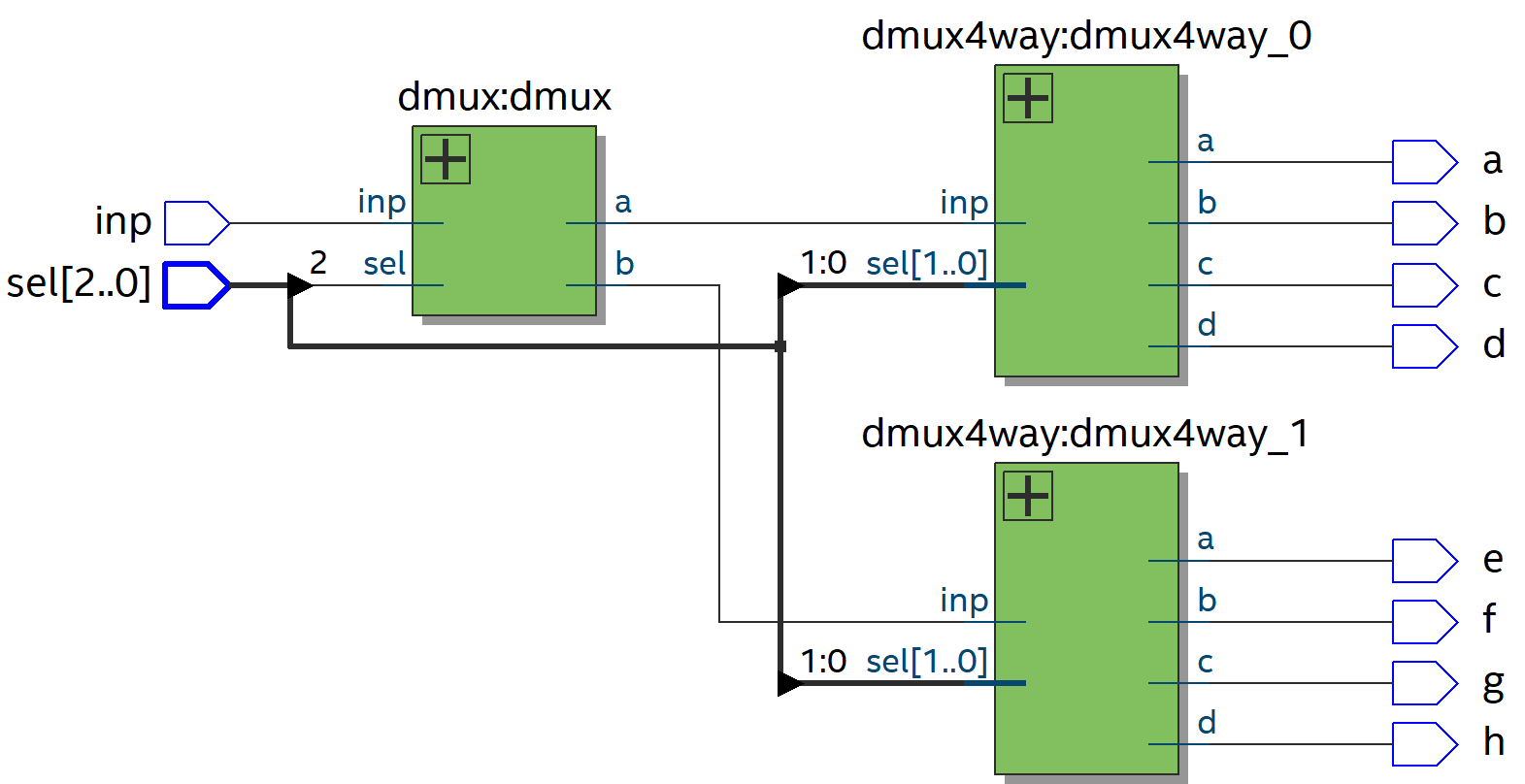

dmux8way:

library ieee; use ieee.std_logic_1164.all; entity dmux8way is port ( inp: in std_logic; sel: in std_logic_vector(2 downto 0); a, b, c, d, e, f, g, h: out std_logic ); end entity; architecture behavior of dmux8way is signal temp_dmux_0, temp_dmux_1: std_logic; begin dmux: entity work.dmux port map ( inp => inp, sel => sel(2), a => temp_dmux_0, b => temp_dmux_1 ); dmux4way_0: entity work.dmux4way port map ( inp => temp_dmux_0, sel => sel(1 downto 0), a => a, b => b, c => c, d => d ); dmux4way_1: entity work.dmux4way port map ( inp => temp_dmux_1, sel => sel(1 downto 0), a => e, b => f, c => g, d => h ); end architecture;