Chapter 5

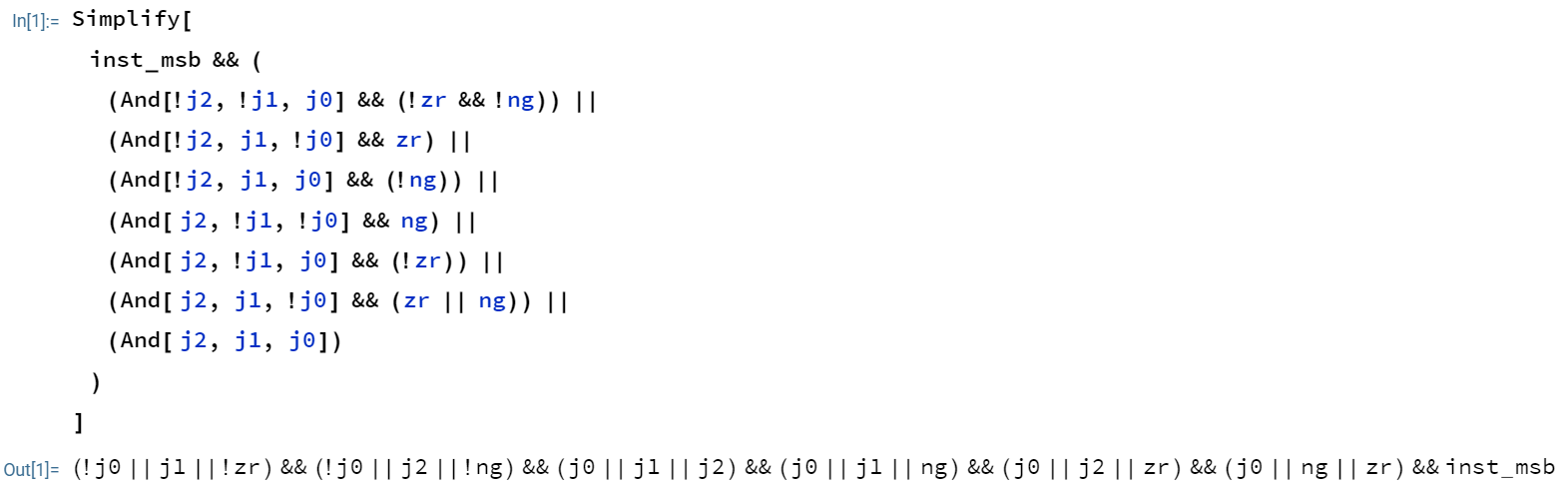

テキストにはほとんど解説がない。ジャンプ命令についてはSimplify[]函数で簡単化した。BooleanMinimize[]函数を使ってもよい。ルールをゆるめてnand以外も使う。

Simplify[ inst_msb && ( (And[!j2, !j1, j0] && (!zr && !ng)) || (And[!j2, j1, !j0] && zr) || (And[!j2, j1, j0] && (!ng)) || (And[ j2, !j1, !j0] && ng) || (And[ j2, !j1, j0] && (!zr)) || (And[ j2, j1, !j0] && (zr || ng)) || (And[ j2, j1, j0]) ) ]

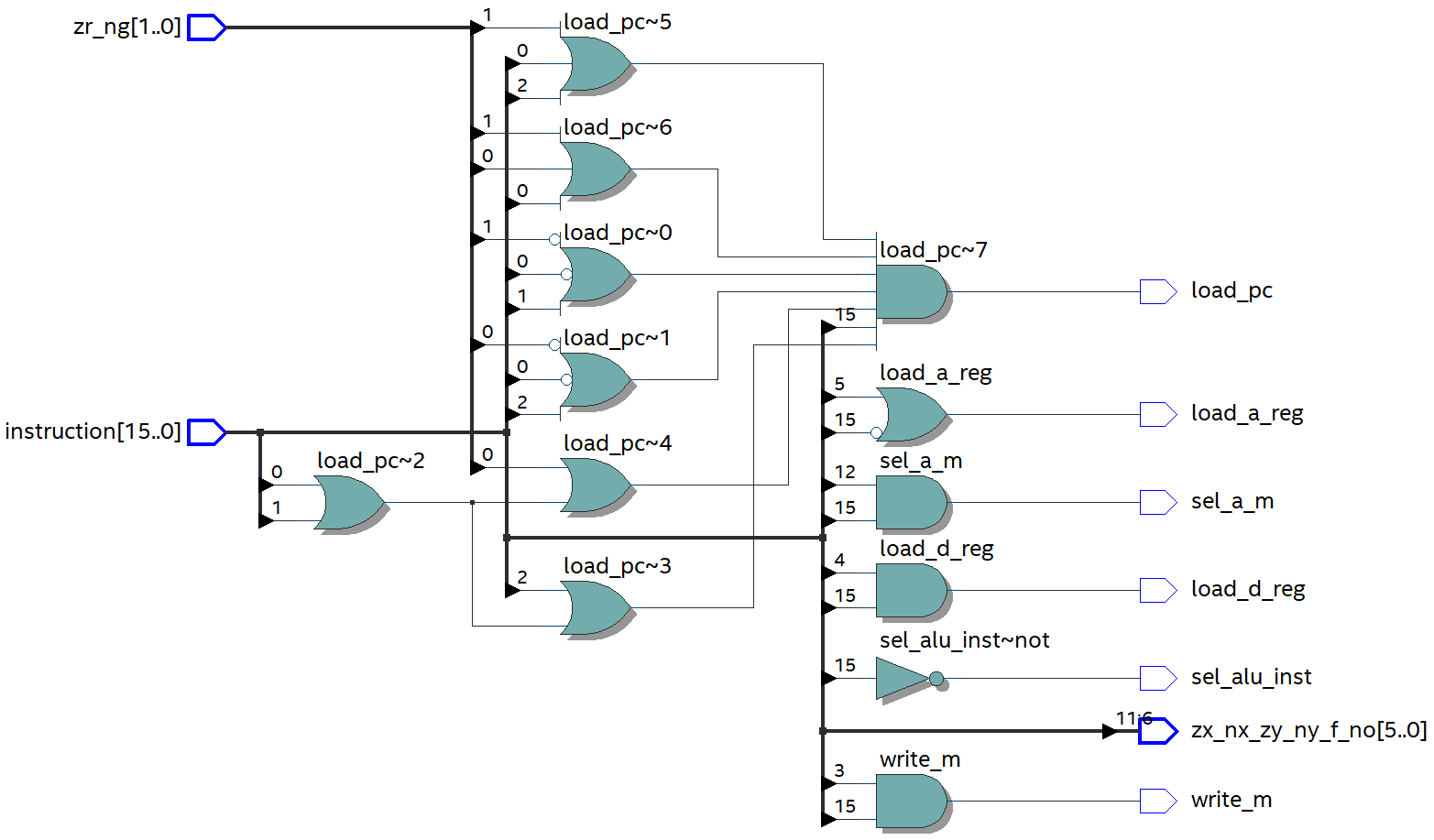

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use ieee.std_logic_misc.all; entity instruction_decoder is port ( instruction: in std_logic_vector(15 downto 0); zr_ng: in std_logic_vector(1 downto 0); sel_alu_inst: out std_logic; sel_a_m: out std_logic; load_a_reg: out std_logic; load_d_reg: out std_logic; load_pc: out std_logic; write_m: out std_logic; zx_nx_zy_ny_f_no: out std_logic_vector(5 downto 0) ); end entity; architecture behavior of instruction_decoder is alias zr is zr_ng(1); alias ng is zr_ng(0); alias inst_msb is instruction(instruction'length-1); alias a is instruction(12); alias cccccc: std_logic_vector(5 downto 0) is instruction(11 downto 6); alias ddd: std_logic_vector(2 downto 0) is instruction(5 downto 3); alias jjj: std_logic_vector(2 downto 0) is instruction(2 downto 0); begin -- a命令のときはinstをa regへ渡す。 -- c命令のときはalu_outをa regへ渡す。 sel_alu_inst <= not inst_msb; sel_a_m <= a and inst_msb; -- c命令であり、かつストア先がa regのときに1を立てて、次のクロックでa regを更新する。 -- またはa命令であるときに1を立てて、次のクロックでa regを更新する。 load_a_reg <= ddd(2) or not inst_msb; load_d_reg <= ddd(1) and inst_msb; write_m <= ddd(0) and inst_msb; zx_nx_zy_ny_f_no <= cccccc; load_pc <= (not jjj(0) or jjj(1) or not zr) and (not jjj(0) or jjj(2) or not ng) and ( jjj(0) or jjj(1) or jjj(2)) and ( jjj(0) or jjj(1) or ng) and ( jjj(0) or jjj(2) or zr) and ( jjj(0) or ng or zr) and inst_msb; end architecture;